RP2040 - разбираем даташиты. Часть 2: Описание системы

Содержание:

Часть 1.4: РаспиновкаВ этой главе описаны ключевые особенности системы RP2040, включая процессор, память, способ подключения блоков, тактовую частоту, сброс, питание и ввод-вывод. См. обзорную диаграмму на Рисунке 2.

2.1 Шина данных

Шина RP2040 маршрутизирует адреса и данные через микросхему.

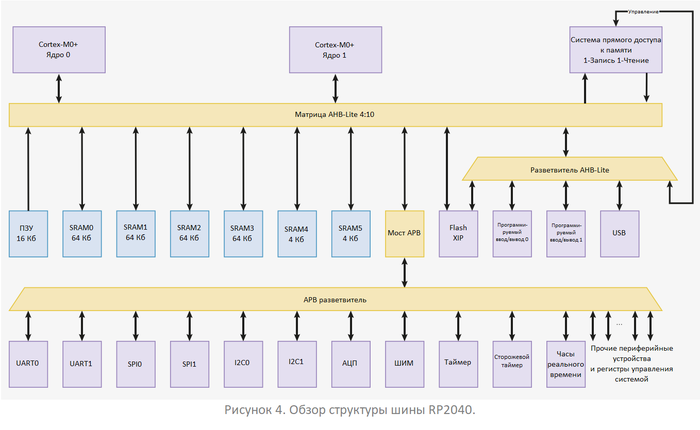

На рисунке 4 показана высокоуровневая структура коммутационной сети шины. Основная матрица AHB-Lite направляет адреса и данные между своими 4 восходящими портами и 10 нисходящими портами: в каждом цикле может происходить до четырех передач по шине. Все тракты данных имеют ширину 32 бита. Устройства памяти имеют выделенные порты на главной панели, чтобы удовлетворить их требования к высокой пропускной способности. Периферийные устройства AHB-Lite с высокой пропускной способностью имеют общий порт на кросс-панели, а мост APB обеспечивает доступ по шине к регистрам управления системой и периферийным устройствам с низкой пропускной способностью.

Структура шины соединяет 4 мастера AHB-Lite, то есть устройства, которые генерируют адреса:

- Ядро процессора 0

- Ядро процессора 1

- Порт чтения на контроллере прямого доступа к памяти

- Порт записи на контроллере прямого доступа к памяти

Они соединены с 10 нисходящими портами на главной шине:

- Постоянное запоминающее устройство (ПЗУ)

- Память с поддержкой функции исполнения на месте (Flash XIP)

- Статическая память с произвольным доступом (SRAM) по одному модулю на порт (0-5)

- Периферийные устройства Fast AHB-Lite: контроллеры программируемого ввода/вывода (PIO0, PIO1), универсальная последовательная шина (USB), регистры управления прямым доступом к памяти и исполнению на месте (один общий порт)

- Мост ко всем периферийным устройствам APB и регистрам управления системой

Четыре мастера шины могут получить доступ к любым четырем различным портам матрицы одновременно, структура шины не добавляет состояния ожидания при любом принудительном доступе через AHB-Lite. Таким образом, при системной частоте 125 МГц, максимальная устойчивая пропускная способность шины составляет 2,0 ГБ/с. Карта адресов системы организована таким образом, чтобы сделать эту параллельную полосу пропускания доступной как можно большему количеству программных вариантов использования - например, чередующийся псевдоним SRAM (раздел 2.6.2) распределяет доступ к основной памяти по четырем портам матрицы (SRAM0… 3), поэтому большее количество обращений к памяти может происходить параллельно.

Arduino & Pi

1.5K постов20.8K подписчика

Правила сообщества

В нашем сообществе запрещается:

• Добавлять посты не относящиеся к тематике сообщества, либо не несущие какой-либо полезной нагрузки (флуд)

• Задавать очевидные вопросы в виде постов, не воспользовавшись перед этим поиском

• Выкладывать код прямо в посте - используйте для этого сервисы ideone.com, gist.github.com или схожие ресурсы (pastebin запрещен)

• Рассуждать на темы политики

• Нарушать установленные правила Пикабу